Въведение

Обикновено при проектиране на интегрирана схема се използват някои математически методи (като двоични диаграми на решения, проблеми с булевата задоволимост) за извършване на формална проверка между различни схеми. Сравнете дали са еквивалентни по отношение на поведението.

Формална проверка

В процеса на проектиране на компютърен хардуер (особено интегрирани схеми) и софтуерни системи, значението наформална проверкасе основава на сигурно или сигурно. За тези формални норми или атрибути се използват математически методи за доказване на тяхната коректност или некоректност.

Softwaretestingcannotprovethatthesystemdoesnothavedefects,norcanitprovethatitmatchescertainattributes.Onlyaformalverificationprocesscanprovethatasystemdoesnothaveacertaindefectormatchesacertainattributeorattributes.Thesystemcannotbeprovenortestedasdefect-free,becauseitisimpossibletoformallystipulatewhatis"nodefect".Allthatcanbedoneistoprovethatasystemdoesnothaveanyconceivabledefectsandsatisfiesalltherequiredandusefulattributesthatmakethesystemmatchthefunction.

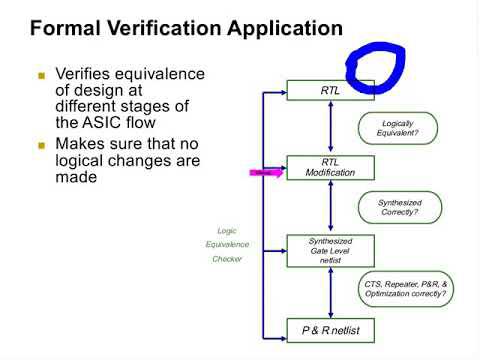

Inintegratedcircuitdesign,formalverificationisaverificationmethodforintegratedcircuitdesign.Itsmainideaistoverifythecorrectnessofadesignbyusingformalverification.Formalverificationcanbedividedintothreecategories:EquivalenceChecking,FormalModelChecking(alsoknownasfeaturechecking)andTheoryProver.

Theverificationofequivalencecheckisusedtoverifytheconsistencybetweentheregistertransferleveldesignandthegate-levelnetlist,andbetweenthegate-levelnetlistandthegate-levelnetlist.Intheprocessofscanchainrearrangement,clocktreesynthesis,etc.,equivalencecheckscanbeusedtoensuretheconsistencyofthenetlist.Equivalencecheckinghasbeenintegratedintotheintegratedcircuitstandarddesignprocess.EquivalencecheckisveryusefulwhencheckingECO.Forexample,whenadesignerismodifyingagate-levelnetlist,hemistakenlywritesanORgateasaNORgateduetoahanderror.Theequivalencechecktoolcaneasilyfindthisbycomparingtheregistertransfer-leveldesignwiththegate-levelnetlist.mistake.

Modelcheckingusestemporallogictodescribespecifications,anduseseffectivesearchmethodstocheckwhetheragivensystemmeetsthespecifications.Modelcheckingisahotspotincurrentresearch,buttheproblemoflimitedcircuitscaleforverificationhasnotbeenwellresolved.

Thetheoremprovesthatboththesystemandthenormareexpressedasmathematicallogicformulas,andthedescriptionissoughtfromtheaxioms.Thetheoremprovesthatthecircuitmodeltobeverifiedisnotlimited,butitrequiresmanualinterventionandmorebackgroundknowledgeoftheuser.

Автоматизация на електронното проектиране

Автоматизация на електронното проектиране(на английски:Electronicdesignautomation, съкращение:EDA) се отнася доизползването на софтуер за компютърно проектиране (CAD) за завършване на дизайна на функционалния дизайн, синтез, проверка, физически дизайн (включително оформление, окабеляване, оформление, проверка на правилата на дизайна и т.н.) на чипове с много големи интегрални схеми (VLSI).

Nowadays,digitalcircuitsareverymodular(seeintegratedcircuitdesign,designclosure,designflow(EDA)).Theforefrontoftheproductionlinestandardizesthedesignprocessanddividesthedesignprocessintomany"cells"(cells).),withoutconsideringtechnologyforthetimebeing,andthencellsusespecificintegratedcircuittechnologytoimplementlogicorotherelectronicfunctions.Manufacturersusuallyprovidelibrariesofcomponentsandsimulationmodelsthatconformtostandardsimulationtoolsfortheproductionprocess.TheanalogEDAtoolislessmodular,becauseitrequiresmorefunctionsandmoreinteractionbetweenparts,andpartsaregenerallylessideal.

Intheelectronicsindustry,duetotheincreasingscaleofthesemiconductorindustry,EDAplaysanincreasinglyimportantrole.Manufacturersusingthistechnologyaremostlyfoundrymanufacturersengagedinthemanufactureofsemiconductordevices,aswellasdesignservicecompaniesthatuseEDAsimulationsoftwaretoevaluateproductionconditions.EDAtoolsarealsousedintheprogrammingoffieldprogrammablelogicgatearrays.