Úvod

Při návrhu integrovaného obvodu se obvykle používají některé matematické metody (jako binární diagramy rozhodování, Booleovy problémy se splněním) k provedení formálního ověření mezi různými obvody. Porovnejte, zda jsou v chování ekvivalentní.

Formální ověření

V procesu návrhu počítačového hardwaru (zejména integrovaných obvodů) a softwarových systémů je významformálního ověřenízaložen na určitých nebo jistýchPro tyto formální normy nebo atributy se používají matematické metody k ověření jejich správnosti nebo správnosti.

Softwaretestingcannotprovethatthesystemdoesnothavedefects,norcanitprovethatitmatchescertainattributes.Onlyaformalverificationprocesscanprovethatasystemdoesnothaveacertaindefectormatchesacertainattributeorattributes.Thesystemcannotbeprovenortestedasdefect-free,becauseitisimpossibletoformallystipulatewhatis"nodefect".Allthatcanbedoneistoprovethatasystemdoesnothaveanyconceivabledefectsandsatisfiesalltherequiredandusefulattributesthatmakethesystemmatchthefunction.

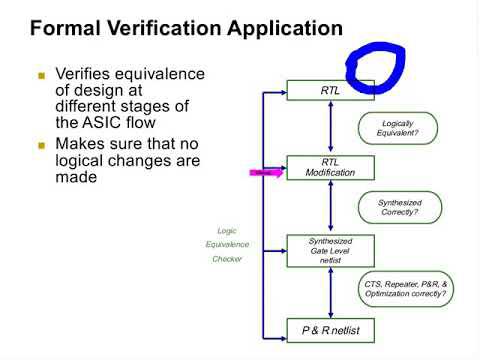

Inintegratedcircuitdesign,formalverificationisaverificationmethodforintegratedcircuitdesign.Itsmainideaistoverifythecorrectnessofadesignbyusingformalverification.Formalverificationcanbedividedintothreecategories:EquivalenceChecking,FormalModelChecking(alsoknownasfeaturechecking)andTheoryProver.

Theverificationofequivalencecheckisusedtoverifytheconsistencybetweentheregistertransferleveldesignandthegate-levelnetlist,andbetweenthegate-levelnetlistandthegate-levelnetlist.Intheprocessofscanchainrearrangement,clocktreesynthesis,etc.,equivalencecheckscanbeusedtoensuretheconsistencyofthenetlist.Equivalencecheckinghasbeenintegratedintotheintegratedcircuitstandarddesignprocess.EquivalencecheckisveryusefulwhencheckingECO.Forexample,whenadesignerismodifyingagate-levelnetlist,hemistakenlywritesanORgateasaNORgateduetoahanderror.Theequivalencechecktoolcaneasilyfindthisbycomparingtheregistertransfer-leveldesignwiththegate-levelnetlist.mistake.

Modelcheckingusestemporallogictodescribespecifications,anduseseffectivesearchmethodstocheckwhetheragivensystemmeetsthespecifications.Modelcheckingisahotspotincurrentresearch,buttheproblemoflimitedcircuitscaleforverificationhasnotbeenwellresolved.

Thetheoremprovesthatboththesystemandthenormareexpressedasmathematicallogicformulas,andthedescriptionissoughtfromtheaxioms.Thetheoremprovesthatthecircuitmodeltobeverifiedisnotlimited,butitrequiresmanualinterventionandmorebackgroundknowledgeoftheuser.

Elektronická automatizace návrhu

Elektronická automatizace návrhu(anglicky:Electronicdesignautomation, zkratka:EDA) odkazuje na použití softwaru pro počítačově podporované navrhování (CAD) k dokončení návrhu funkčního návrhu, syntéza, ověření, fyzický návrh (včetně uspořádání, zapojení, uspořádání, kontroly pravidel návrhu atd.) čipů s integrovaným obvodem (VLSI) velmi velkého rozsahu.

Nowadays,digitalcircuitsareverymodular(seeintegratedcircuitdesign,designclosure,designflow(EDA)).Theforefrontoftheproductionlinestandardizesthedesignprocessanddividesthedesignprocessintomany"cells"(cells).),withoutconsideringtechnologyforthetimebeing,andthencellsusespecificintegratedcircuittechnologytoimplementlogicorotherelectronicfunctions.Manufacturersusuallyprovidelibrariesofcomponentsandsimulationmodelsthatconformtostandardsimulationtoolsfortheproductionprocess.TheanalogEDAtoolislessmodular,becauseitrequiresmorefunctionsandmoreinteractionbetweenparts,andpartsaregenerallylessideal.

Intheelectronicsindustry,duetotheincreasingscaleofthesemiconductorindustry,EDAplaysanincreasinglyimportantrole.Manufacturersusingthistechnologyaremostlyfoundrymanufacturersengagedinthemanufactureofsemiconductordevices,aswellasdesignservicecompaniesthatuseEDAsimulationsoftwaretoevaluateproductionconditions.EDAtoolsarealsousedintheprogrammingoffieldprogrammablelogicgatearrays.