Johdanto

Yleensä integroidun piirin suunnittelussa käytetään joitakin matemaattisia menetelmiä (kuten binäärisiä päätöskaavioita, Boolen tyydyttävyysongelmia) muodolliseen varmennukseen eri piirien välillä. Vertaa, vastaavatko ne.

Muodollinen varmennus

Tietokonelaitteistojen (erityisesti integroitujen piirien) ja ohjelmistojärjestelmien suunnitteluprosessissamuodollisen vahvistuksen merkitys perustuu tiettyihin tiettyihin näille muodollisille normeille/määritteille, matemaattisia menetelmiä käytetään niiden oikeellisuuden todistamiseen.

Softwaretestingcannotprovethatthesystemdoesnothavedefects,norcanitprovethatitmatchescertainattributes.Onlyaformalverificationprocesscanprovethatasystemdoesnothaveacertaindefectormatchesacertainattributeorattributes.Thesystemcannotbeprovenortestedasdefect-free,becauseitisimpossibletoformallystipulatewhatis"nodefect".Allthatcanbedoneistoprovethatasystemdoesnothaveanyconceivabledefectsandsatisfiesalltherequiredandusefulattributesthatmakethesystemmatchthefunction.

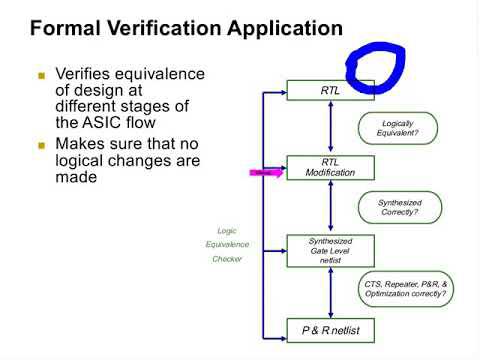

Inintegratedcircuitdesign,formalverificationisaverificationmethodforintegratedcircuitdesign.Itsmainideaistoverifythecorrectnessofadesignbyusingformalverification.Formalverificationcanbedividedintothreecategories:EquivalenceChecking,FormalModelChecking(alsoknownasfeaturechecking)andTheoryProver.

Theverificationofequivalencecheckisusedtoverifytheconsistencybetweentheregistertransferleveldesignandthegate-levelnetlist,andbetweenthegate-levelnetlistandthegate-levelnetlist.Intheprocessofscanchainrearrangement,clocktreesynthesis,etc.,equivalencecheckscanbeusedtoensuretheconsistencyofthenetlist.Equivalencecheckinghasbeenintegratedintotheintegratedcircuitstandarddesignprocess.EquivalencecheckisveryusefulwhencheckingECO.Forexample,whenadesignerismodifyingagate-levelnetlist,hemistakenlywritesanORgateasaNORgateduetoahanderror.Theequivalencechecktoolcaneasilyfindthisbycomparingtheregistertransfer-leveldesignwiththegate-levelnetlist.mistake.

Modelcheckingusestemporallogictodescribespecifications,anduseseffectivesearchmethodstocheckwhetheragivensystemmeetsthespecifications.Modelcheckingisahotspotincurrentresearch,buttheproblemoflimitedcircuitscaleforverificationhasnotbeenwellresolved.

Thetheoremprovesthatboththesystemandthenormareexpressedasmathematicallogicformulas,andthedescriptionissoughtfromtheaxioms.Thetheoremprovesthatthecircuitmodeltobeverifiedisnotlimited,butitrequiresmanualinterventionandmorebackgroundknowledgeoftheuser.

Electronicdesignautomation

Electronicdesignautomation(englanniksi:Electronicdesignautomation, lyhenne:EDA) viittaa tietokoneavusteisen suunnittelun (CAD) käyttämiseen toiminnallisen suunnittelun, synteesi, todentaminen, fyysinen suunnittelu (mukaan lukien layout, johdotukset, layout, suunnittelusääntöjen tarkistus jne.) erittäin suuren mittakaavan integroidun piirin (VLSI) piirien avulla.

Nowadays,digitalcircuitsareverymodular(seeintegratedcircuitdesign,designclosure,designflow(EDA)).Theforefrontoftheproductionlinestandardizesthedesignprocessanddividesthedesignprocessintomany"cells"(cells).),withoutconsideringtechnologyforthetimebeing,andthencellsusespecificintegratedcircuittechnologytoimplementlogicorotherelectronicfunctions.Manufacturersusuallyprovidelibrariesofcomponentsandsimulationmodelsthatconformtostandardsimulationtoolsfortheproductionprocess.TheanalogEDAtoolislessmodular,becauseitrequiresmorefunctionsandmoreinteractionbetweenparts,andpartsaregenerallylessideal.

Intheelectronicsindustry,duetotheincreasingscaleofthesemiconductorindustry,EDAplaysanincreasinglyimportantrole.Manufacturersusingthistechnologyaremostlyfoundrymanufacturersengagedinthemanufactureofsemiconductordevices,aswellasdesignservicecompaniesthatuseEDAsimulationsoftwaretoevaluateproductionconditions.EDAtoolsarealsousedintheprogrammingoffieldprogrammablelogicgatearrays.