Introduction

Usuallyinintegratedcircuitdesign,somemathematicalmethods(suchasbinarydecisiondiagrams,Booleansatisfiabilityproblems)areusedtoperformformalverificationbetweendifferentcircuits.Comparewhethertheyareequivalentinbehavior.

Formalverification

Inthedesignprocessofcomputerhardware(especiallyintegratedcircuits)andsoftwaresystems,themeaningofformalverificationisbasedonacertainoracertainFortheseformalnormsorattributes,mathematicalmethodsareusedtoprovetheircorrectnessorincorrectness.

Softwaretestingcannotprovethatthesystemdoesnothavedefects,norcanitprovethatitmatchescertainattributes.Onlyaformalverificationprocesscanprovethatasystemdoesnothaveacertaindefectormatchesacertainattributeorattributes.Thesystemcannotbeprovenortestedasdefect-free,becauseitisimpossibletoformallystipulatewhatis"nodefect".Allthatcanbedoneistoprovethatasystemdoesnothaveanyconceivabledefectsandsatisfiesalltherequiredandusefulattributesthatmakethesystemmatchthefunction.

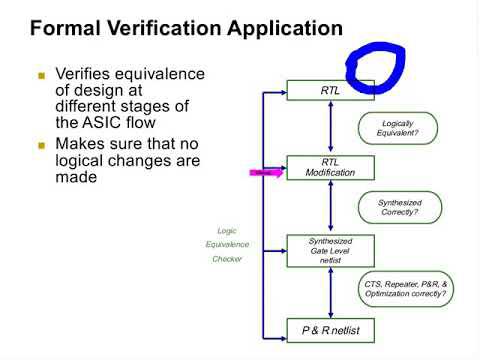

Inintegratedcircuitdesign,formalverificationisaverificationmethodforintegratedcircuitdesign.Itsmainideaistoverifythecorrectnessofadesignbyusingformalverification.Formalverificationcanbedividedintothreecategories:EquivalenceChecking,FormalModelChecking(alsoknownasfeaturechecking)andTheoryProver.

Theverificationofequivalencecheckisusedtoverifytheconsistencybetweentheregistertransferleveldesignandthegate-levelnetlist,andbetweenthegate-levelnetlistandthegate-levelnetlist.Intheprocessofscanchainrearrangement,clocktreesynthesis,etc.,equivalencecheckscanbeusedtoensuretheconsistencyofthenetlist.Equivalencecheckinghasbeenintegratedintotheintegratedcircuitstandarddesignprocess.EquivalencecheckisveryusefulwhencheckingECO.Forexample,whenadesignerismodifyingagate-levelnetlist,hemistakenlywritesanORgateasaNORgateduetoahanderror.Theequivalencechecktoolcaneasilyfindthisbycomparingtheregistertransfer-leveldesignwiththegate-levelnetlist.mistake.

Modelcheckingusestemporallogictodescribespecifications,anduseseffectivesearchmethodstocheckwhetheragivensystemmeetsthespecifications.Modelcheckingisahotspotincurrentresearch,buttheproblemoflimitedcircuitscaleforverificationhasnotbeenwellresolved.

Thetheoremprovesthatboththesystemandthenormareexpressedasmathematicallogicformulas,andthedescriptionissoughtfromtheaxioms.Thetheoremprovesthatthecircuitmodeltobeverifiedisnotlimited,butitrequiresmanualinterventionandmorebackgroundknowledgeoftheuser.

Electronicdesignautomation

Electronicdesignautomation(English:Electronicdesignautomation,abbreviation:EDA)referstotheuseofcomputer-aideddesign(CAD)softwaretocompletethedesignofthefunctionaldesign,synthesis,verification,physicaldesign(includinglayout,wiring,layout,designrulechecking,etc.)ofverylarge-scaleintegratedcircuit(VLSI)chipsWay.

Nowadays,digitalcircuitsareverymodular(seeintegratedcircuitdesign,designclosure,designflow(EDA)).Theforefrontoftheproductionlinestandardizesthedesignprocessanddividesthedesignprocessintomany"cells"(cells).),withoutconsideringtechnologyforthetimebeing,andthencellsusespecificintegratedcircuittechnologytoimplementlogicorotherelectronicfunctions.Manufacturersusuallyprovidelibrariesofcomponentsandsimulationmodelsthatconformtostandardsimulationtoolsfortheproductionprocess.TheanalogEDAtoolislessmodular,becauseitrequiresmorefunctionsandmoreinteractionbetweenparts,andpartsaregenerallylessideal.

Intheelectronicsindustry,duetotheincreasingscaleofthesemiconductorindustry,EDAplaysanincreasinglyimportantrole.Manufacturersusingthistechnologyaremostlyfoundrymanufacturersengagedinthemanufactureofsemiconductordevices,aswellasdesignservicecompaniesthatuseEDAsimulationsoftwaretoevaluateproductionconditions.EDAtoolsarealsousedintheprogrammingoffieldprogrammablelogicgatearrays.